## **OPERATOR'S MANUAL**

## TLD 488-16

## INTERACTIVE DIGITAL PROGRAMMER

| KEPCO INC.<br>An ISO 9001 Company. | TLD 4     | MODEL TLD 488-16 DIGITAL PROGRAMMER |  |  |  |  |

|------------------------------------|-----------|-------------------------------------|--|--|--|--|

|                                    | ORDER NO. | REV. NO.                            |  |  |  |  |

|                                    |           |                                     |  |  |  |  |

#### IMPORTANT NOTES:

1) This manual is valid for the following Model and associated serial numbers:

MODEL SERIAL NO. REV. NO.

- A Change Page may be included at the end of the manual. All applicable changes and revision number changes are documented with reference to the equipment serial numbers. Before using this Operator's Manual, check your equipment serial number to identify your model. If in doubt, contact your nearest Kepco Representative, or the Kepco Documentation Office in New York, (718) 461-7000, requesting the correct revision for your particular model and serial number.

- The contents of this manual are protected by copyright. Reproduction of any part can be made only with the specific written permission of Kepco, Inc.

Data subject to change without notice.

©2000, KEPCO, INC. P/N 243-0736

## **TABLE OF CONTENTS**

| PARA | GRAPH                                                                                  | PAGE       |

|------|----------------------------------------------------------------------------------------|------------|

|      | SECTION I—INTRODUCTION                                                                 |            |

| 1-1  | Scope of Manual                                                                        | 1-1        |

| 1-3  | General Description                                                                    | 1-1        |

| 1-8  | Specifications, General                                                                | 1-2        |

| 1-9  | Specifications, Plug-in Cards                                                          | 1-2        |

| 1-10 | Block Diagram Description                                                              | 1-3        |

|      | SECTION II—PREPARATION FOR USE                                                         |            |

| 2-1  | Unpacking and Inspection                                                               | 2-1        |

| 2-4  | Installation                                                                           | 2-1        |

| 2-6  | Set Device Address, Reset Function and Shield Ground                                   | 2-1        |

| 2.8  | Set TL 488-4A or TL 488-4B Board Addresses and Power Supply Identification Switches    | 2-3        |

| 2-10 | Set A-C Line Voltage                                                                   | 2-6        |

| 2.11 | Installation of the Model TLD 488–16                                                   | 2-6        |

| 2-13 | Preparation and Installation of Kepco Series PCA Cable Assemblies (ATE Power Supplies) | 2-6        |

| 2-15 | Installation of PCA X-3 and Cable (BOP Power Supplies) with TL 488-4B Boards           | 2-8        |

| 2-18 | Final Systems Interconnections                                                         | 2-8        |

|      | SECTION III—OPERATION                                                                  |            |

| 3-1  | General                                                                                | 3-1        |

| 3-3  | Communications                                                                         | 3-1        |

| 3-6  | CIIL Codes                                                                             | 3-2        |

| 3-8  | The FUNCTION Command                                                                   | 3-2        |

| 3-10 | The SET, SRX and SRN Commands                                                          | 3-3        |

| 3-12 | The OPEN/CLOSE Relay Commands                                                          | ა-ა<br>ი ი |

| 3-14 | The RESET Command                                                                      | ن-ن<br>د د |

| 3-16 | The CONFIDENCE TEST Command                                                            | 7-∆        |

| 3-18 | The INTERNAL SELF-TEST Command                                                         | 3-4        |

| 3-20 | The STATUS Command  Error Handling Commands                                            | 3-4        |

| 3-22 | Bus Transmission Format                                                                | 3-4        |

| 3-24 | Response Message Syntax                                                                | 3-5        |

| 3-27 | Catastrophic Error Handling, Mate Systems and Non-Mate Systems                         | 3-6        |

| 3-34 | General Programming Comments                                                           | 3-7        |

| 3-40 | A Programming Example in Commodore Basic                                               | 3-8        |

| 3-51 | System Calibration                                                                     | 3-11/3-12  |

|      | APPENDIX A                                                                             |            |

|      | E-Prom Changes                                                                         | A1,A2      |

## LIST OF ILLUSTRATIONS

| FIGUE | RE                                                                                                        | PAGE      |

|-------|-----------------------------------------------------------------------------------------------------------|-----------|

| 1-1   | Kepco Model TLD 488-16 Interacting Digital Programmer                                                     | iii/iv    |

| 1-2   | Block Diagram of a Typical Test-Set-Up                                                                    | 1-3       |

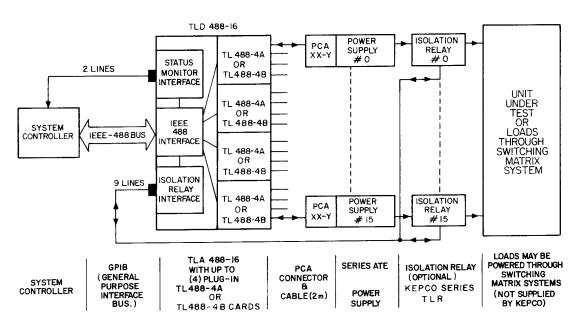

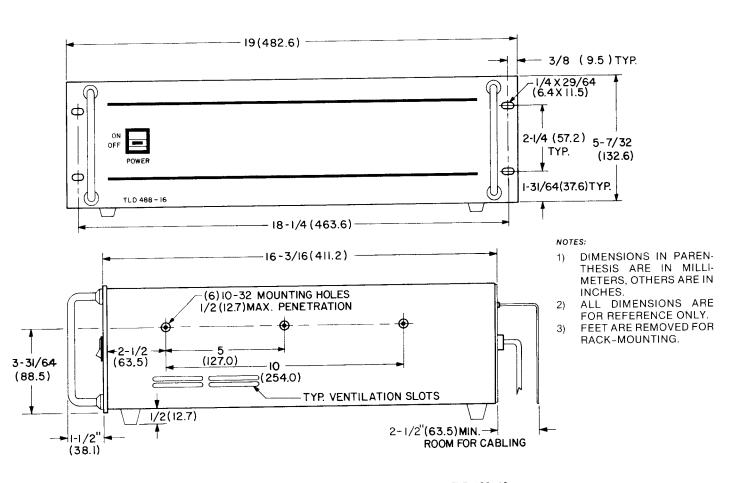

| 1-3   | Mechanical Outline Drawing                                                                                | 1-4       |

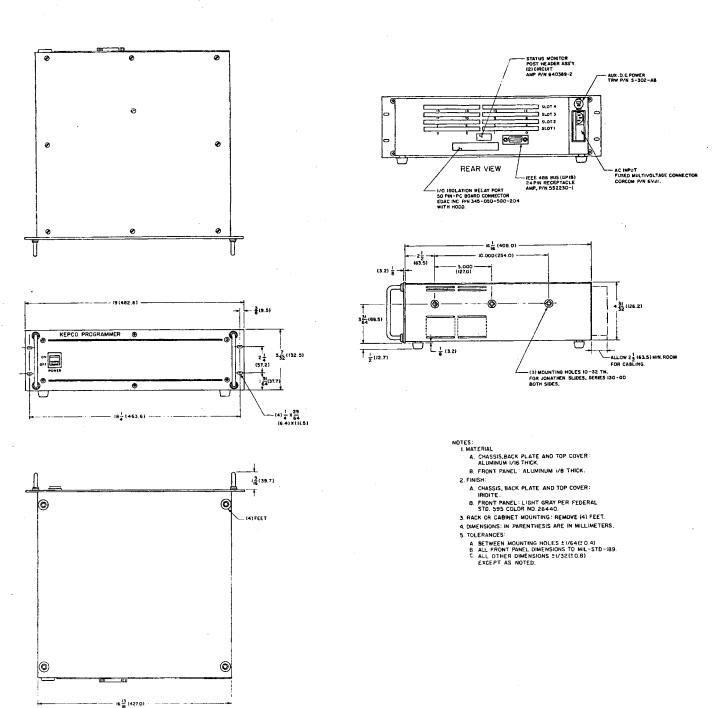

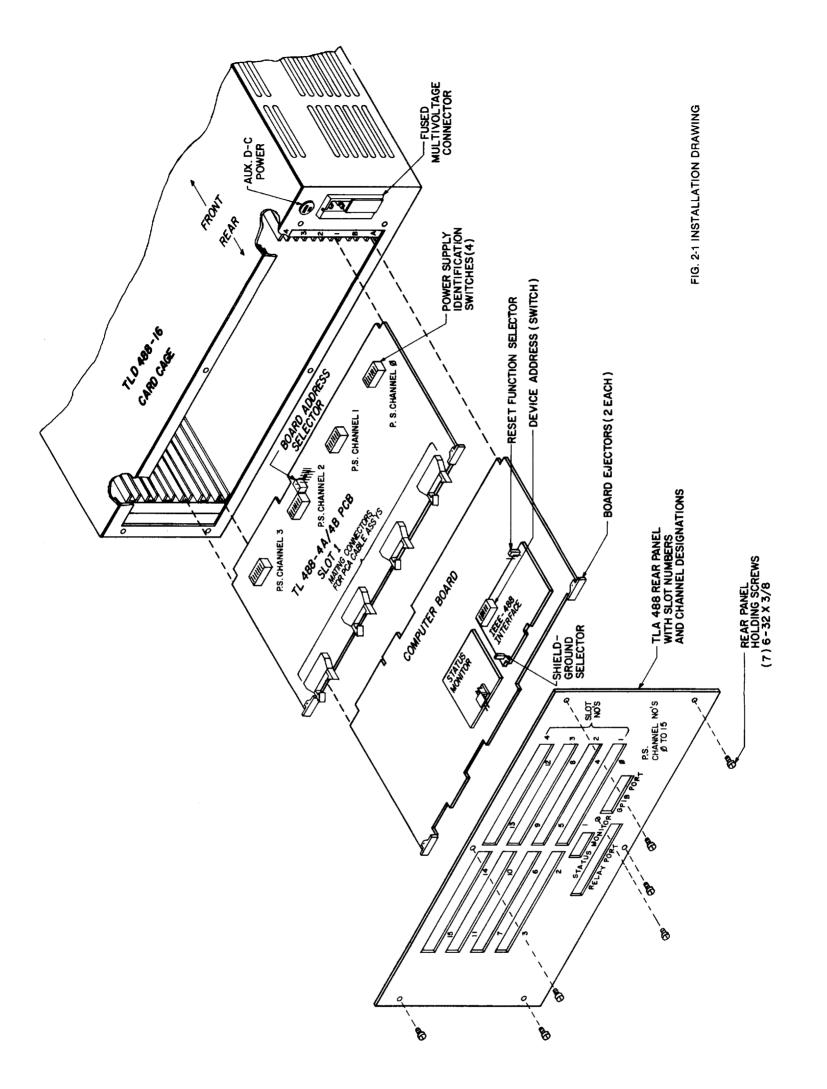

| 2-1   | Installation Drawing, Kepco Model TLD 488-16                                                              | 2-11/2-12 |

| 2-2   | IEEE 488 Interface Board, Device Selector Details                                                         | 2-1       |

| 2-3   | View of TL 488-4A and TL 488-4B, with Board Address Selector Detail                                       | 2-3       |

| 2-4   | One of Four Power Supply Identification Switches on the TL 488-4A and TL 488-4B Boards                    | 2-3       |

| 2-5   | Installation of the Model TLD 488–16                                                                      | 2-6       |

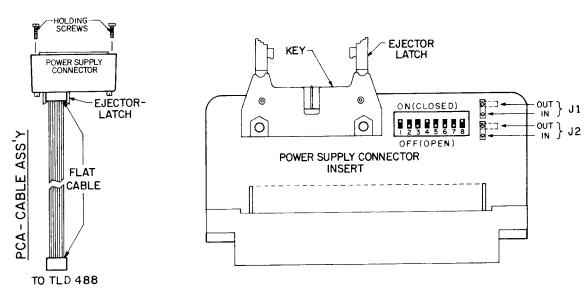

| 2-6   | PCA Power Supply Connector Insert. Top View                                                               | 2-/       |

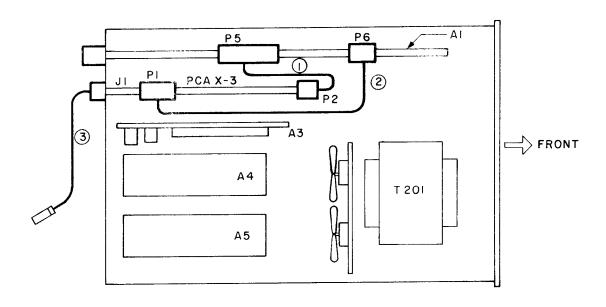

| 2-7   | ROP Power Supply, Top-View (Simplified) with PCA X-3 Interface Installed                                  | 2-8       |

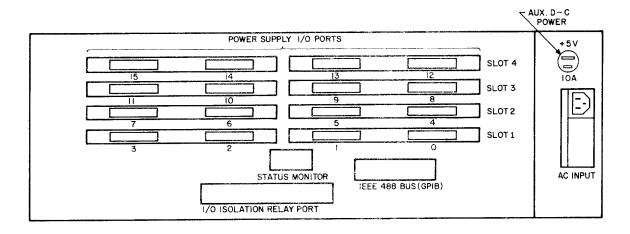

| 2-8   | Model TLD 488-16 Rear Terminations                                                                        | 2-9       |

| 2-9   | Relay Port, Pin-Outs                                                                                      | 2-10      |

| 2-10  | Timing Diagram, I/O Isolation Relay Port                                                                  | 2-10      |

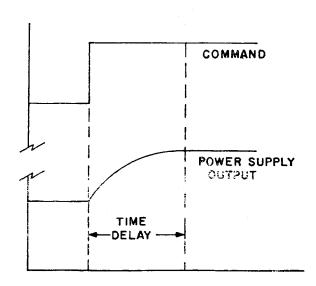

| 3-1   | Relationship of INPUT command and Power Supply Output                                                     | 3-7       |

| 3-2   | Listing of Example Program                                                                                |           |

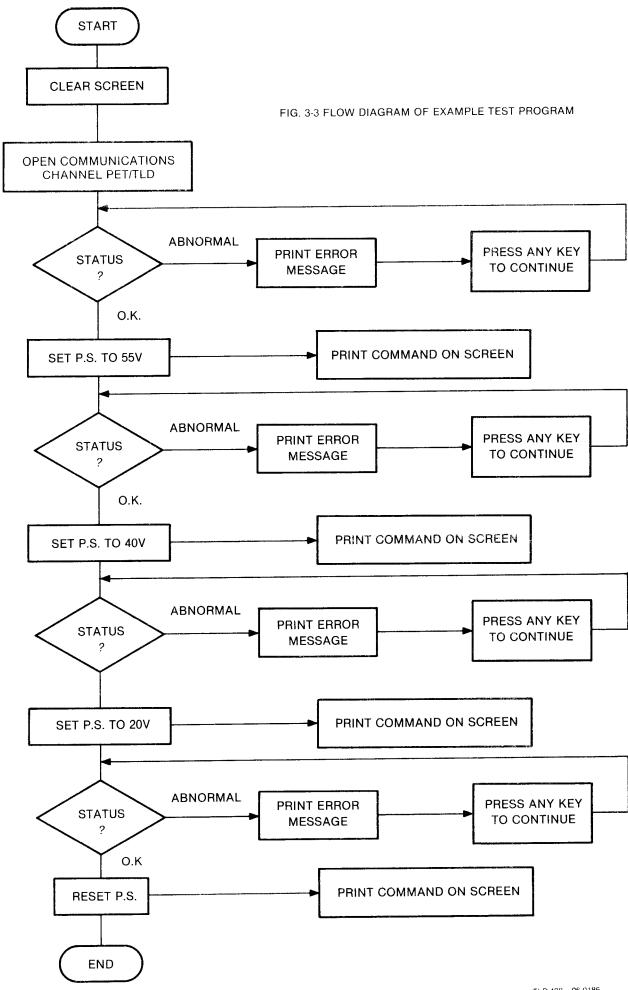

| 3-3   | Logic Flow Diagram of Example Program                                                                     | 3-10      |

|       | LIST OF TABLES                                                                                            |           |

| TABL  |                                                                                                           | PAGE      |

|       |                                                                                                           | 1-1       |

| 1-1   | TLD 488–16 Interface Functions                                                                            | 1-1       |

| 1-2   | Series PCA Connector Assemblies for ATE Power Supplies                                                    | 1-2       |

| 1-3   | General Specifications Model TLD 488–16<br>Specifications for Model TL 488–4A and TL 488–4B Plug-In Cards | 1-2       |

| 1-4   |                                                                                                           |           |

| 2-1   | Device Address Selection on the Kepco Model TLD 488-16                                                    | 2-2       |

| 2-2   | Model Table for Setting the Power Supply Identification Switches on the 1L 488-4A Board                   |           |

| 2-3   | Model Table for Setting the Power Supply Identification Switches on the TL 488-4B Board                   | ∠-∵       |

| 2-4   | Switch and Jumper Selection on the PCA-1 for 1/4-Rack ATE Power Supplies                                  |           |

| 2-5   | Switch and Jumper Selection on the PCA-2 for ½, ¾ and Full Rack ATE Power Supplies                        | 2-7       |

| 3-1   | Interface Functions Implemented by the TLD 488-16                                                         | 3-1       |

| 3-1   | Mosasages Sept or Received by the TLD 488-16 in Command Mode                                              | ۱ -د      |

| 3-2   | Messages Sent or Received by the TLD 488-16 in Data Mode                                                  | 2         |

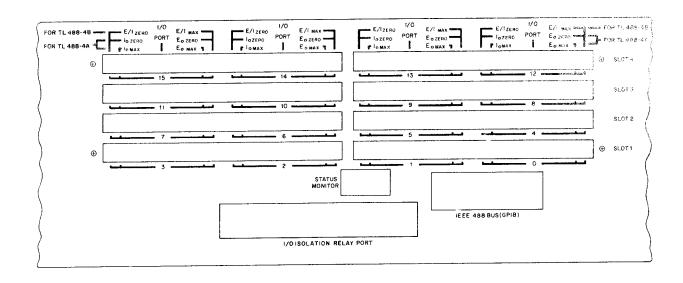

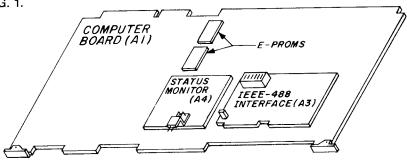

FIG. 1-1 KEPCO MODEL TLD 488-16 INTERACTING DIGITAL PROGRAMMER, FRONT AND REAR VIEW.

## SECTION I—INTRODUCTION

#### 1-1 SCOPE OF MANUAL

1-2 This operator's manual contains the specifications and instructions for the installation and operation of the Model TLD 488–16 Digital Programmer, manufactured by Kepco Inc., Flushing, N.Y., U.S.A. For extended technical information see the Kepco TLD 488–16 Hardware Reference Manual.

## 1-3 GENERAL DESCRIPTION (See Fig. 1-1)

- 1-4 The Kepco Model TLD 488–16, was designed as an interactive digital to analog interface between a system controller and the Kepco Series ATE and BOP power supplies. The TLD 488–16 communicates with its controller via the IEEE 488 (GPIB) bus and is designated as a LISTENER or a TALKER according to the GPIB protocol. The TLD 488–16 recognizes and responds to the mnemonics and syntax of the Control Interface Intermediate Languague (CIIL). It uses a built-in microprocessor to drive up to four plug-in cards which in turn can control up to four power supplies each, so that a single TLD 488–16 can control up to sixteen power supplies. The TLD 488–16 recognizes ten commands: FUNCTION, SET, SET MAXIMUM, SET MINIMUM, CLOSE, OPEN, RESET, INTERNAL SELF TEST, CONFIDENCE TEST and STATUS. It also recognizes five nouns and noun modifiers: DIRECT CURRENT SOURCE, VOLTAGE, VOLTAGE LIMIT, CURRENT and CURRENT LIMIT. When the TLD 488–16 is "talk addressed" by the controller over the IEEE 488 bus, it will respond with an error message if it can not comply with the instruction. Some possible error messages are: CROWBARRED, OVERLOAD, VOLTAGE COMPARISON ERROR, CURRENT COMPARISON ERROR, DEVICE NOT PRESENT and INVALID COMMAND.

- 1-5 The interface functions implemented by Kepco's TLD 488-16 on the GENERAL PURPOSE INTERFACE BUS (GPIB), as defined by the IEEE-488 Standard, are listed in Table 1-1.

| GPIB FUNCTION      | SUBSET<br>SYMBOL | COMMENTS                                     |  |  |

|--------------------|------------------|----------------------------------------------|--|--|

| Source Handshake   | SH1              |                                              |  |  |

| Acceptor Handshake | AH1              |                                              |  |  |

| Talker             | Т6               | Basic talker, serial poll, unaddress if MLA. |  |  |

| Listener           | L4               | Basic listener,<br>unaddress if MTA.         |  |  |

| Service Request    | SR1              |                                              |  |  |

| Device Clear       | DC1              |                                              |  |  |

| TABLE 1-1 TLD 488-16 INTERFACE FUNCTIONS |

|------------------------------------------|

|------------------------------------------|

| OUTPUT<br>VOLTAGE<br>RATING | ATE 1/4 RACK<br>50W & 100W<br>SIZES A & B | ATE ½, ¾ & FULL RACK<br>250W, 500W & 1000W<br>SIZES C, D & E |

|-----------------------------|-------------------------------------------|--------------------------------------------------------------|

| 6V                          | PCA 6-1                                   | PCA 6-2                                                      |

| 15V                         | PCA 15-1                                  | PCA 15-2                                                     |

| 25V                         | PCA 25-1                                  | PCA 25-2                                                     |

| 36V                         | PCA 36-1                                  | PCA 36-2                                                     |

| 55V                         | PCA 55-1                                  | PCA 55-2                                                     |

| 75V                         | PCA 75-1                                  | PCA 75-2                                                     |

| 100V                        | PCA 100-1                                 | PCA 100-2                                                    |

| 150V                        | PCA 150-1                                 | PCA 150-2                                                    |

| 325V                        | N.A.                                      | PCA 325-2                                                    |

TABLE 1-2 SERIES PCA CONNECTOR ASSEMBLIES FOR ATE UNIPOLAR POWER SUPPLIES

- In order to interconnect the TLD 488–16 with ATE power supplies, a Kepco Series PCA interface connector must be selected for each power supply from Table 1-2. For BOP power supplies, a single interface is used, Model PCA X-3, which is mounted inside the BOP. The interconnection from the TLD 488–16 to the GPIB is made with an IEEE 488 standard bus cable. The TLD 488–16 has a separate input/output port to close, open and verify the status of external relays which may be connected between the power supplies and the load. In addition, a status monitor port is available which provides a two-wire status monitor line to the controller to report catastrophic failures in the TLD 488–16 or in the power supplies. Connectors for the STATUS MONITOR INTERFACE and the ISOLATION RELAY INTERFACE are provided.

- 1-7 The TLD 488-16 consists of a "full-rack" (19 inch) standard card cage. It contains a single-board micro-computer and accomodates up to four (4) plug-in cards. These cards may either be Model TL 488-4A (for ATE power supplies), or Model TL 488-4B (for BOP power supplies), or a mixture of the two. Each plug-in card can control the voltage and current function of up to four (4) power supplies. With a full complement of four (4) TL 488-4A or TL 488-4B cards, the system will control 16 individual, isolated, power supplies.

### 1-8 SPECIFICATIONS, GENERAL: Refer to Table 1-3

| A-C Input requirements:              | 105 to 125V a-c or 210 to 250V a-c<br>Approximately 90W maximum                 |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Ambient operating temperature range: | 0°C to +55°C                                                                    |  |  |  |  |

| Storage temp. range:                 | – 20°C to +75°C                                                                 |  |  |  |  |

| Dimensions:                          | 5 <sup>7</sup> / <sub>32</sub> "H, x 19"W, x 16 <sup>3</sup> / <sub>16</sub> "D |  |  |  |  |

| Weight:                              | Approximately 8 lbs.                                                            |  |  |  |  |

| Color:                               | Gray, Fed. Std. 26440                                                           |  |  |  |  |

| Mounting:                            | 19" rack (Provisions for chassis slides.)                                       |  |  |  |  |

TABLE 1-3 GENERAL SPECIFICATIONS MODEL TLD 488-16

## 1-9 SPECIFICATIONS, PLUG-IN CARDS: Refer to Table 1-4

| MODEL                                                  | TL 488-4A                                                                                                                                          | TL 488-4B                                                                                                                             |  |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Number of isolated input/output ports                  | Four (                                                                                                                                             | 4) ports.                                                                                                                             |  |  |  |  |  |  |

| Analog outputs per port                                | Two (2)                                                                                                                                            | Two (2) channels.                                                                                                                     |  |  |  |  |  |  |

| Mode of operation<br>for the Analog<br>Output Channels | Voltage and Current Limit or<br>Current and Voltage Limit.<br>Determined by noun modifiers<br>within SET command.                                  |                                                                                                                                       |  |  |  |  |  |  |

| Analog output voltage level                            | 0 to +10V for Voltage<br>or Voltage Limit Channel<br>0 to +1V for Current or<br>Current Limit Channel.                                             | 0 to ± 10V Main Channel 0 to + 10V Limit Channel                                                                                      |  |  |  |  |  |  |

| Analog output current level                            | 0 to +2mA<br>per channel.                                                                                                                          | 0 to ±2mA Main Channel<br>0 to +2mA Limit Channel                                                                                     |  |  |  |  |  |  |

| Output impedance                                       |                                                                                                                                                    | 5 ohms.                                                                                                                               |  |  |  |  |  |  |

| Output resolution                                      | 12 bit.                                                                                                                                            |                                                                                                                                       |  |  |  |  |  |  |

| Linearity error<br>(0 to +55°C)                        | < ± ½ LSB. (Lea                                                                                                                                    | ast Significant Bit)                                                                                                                  |  |  |  |  |  |  |

| Adjustments                                            | Full Scale calibration.<br>Zero adjustment. Both channels                                                                                          | Main Channel only                                                                                                                     |  |  |  |  |  |  |

| Temp. coefficient (per degree C)                       |                                                                                                                                                    | at full scale.<br>/ at zero.                                                                                                          |  |  |  |  |  |  |

| Isolation<br>between ports                             |                                                                                                                                                    | V d-c.                                                                                                                                |  |  |  |  |  |  |

| Power supply identification codes                      |                                                                                                                                                    | P switches for<br>h port.                                                                                                             |  |  |  |  |  |  |

| Input signals accepted from the power supply           | Supply Absent flag. Voltage/Current Mode flag. Crowbar flag. Voltage out of limit (0.1% of full scale). Current out of limit (1.0% of full scale). | Supply Absent flag. Overload flag. Turn-off flag. Voltage out of limit (0.1% of full scale) Current out of limit (0.1% of full scale) |  |  |  |  |  |  |

| Input digital commands                                 | Via Multibus™<br>All signals T                                                                                                                     | from TLD 488–16.<br>TL compatible.                                                                                                    |  |  |  |  |  |  |

| Power requirements                                     | from TI                                                                                                                                            | via Multibus™<br>_D 488-16.                                                                                                           |  |  |  |  |  |  |

| Card, physical characteristics                         | Width: 12''.<br>Height: 0.5''. W                                                                                                                   | Width: 12''. Length 6.75''.<br>Height: 0.5''. Weight: 20 ounces.                                                                      |  |  |  |  |  |  |

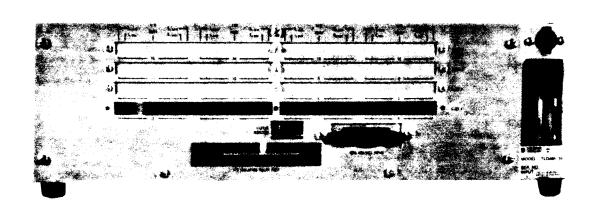

### 1-10 BLOCK DIAGRAM DESCRIPTION (Refer to FIG. 1-2)

FIG. 1-2 BLOCK DIAGRAM OF A TYPICAL TEST SET-UP, SHOWING THE INTERFACE CONNECTIONS BETWEEN A SYSTEM CONTROLLER, THE KEPCO MODEL TLD 488-16 AND KEPCO SERIES ATE or BOP POWER SUPPLIES.

- 1-11 The BLOCK DIAGRAM (FIG. 1-2) shows a typical test set up under the direction of a SYSTEM CON-TROLLER. All communications between the TLD 488-16 and the SYSTEM CONTROLLER take place on the IEEE 488 bus. The additional two lines to the SYSTEM CONTROLLER transmit a contact closure in case of a serious malfunction in one of the power supplies. The nine (9) relay lines may be used to operate optional relays (Kepco Series TLR, for example) which isolate the load from the power supplies if required.

- 1-12 The SYSTEM CONTROLLER can set the output voltage with current limit, or the output current with voltage limit for ATE power supplies or the Main Channel and Limit Channel values for BOP power supplies on each of the power supplies connected to the TLD 488-16. The commands to and the response from the power supplies are transmitted via the TLD 488-16 and the IEEE 488 bus, using the mnemonics and syntax of the Control Interface Intermediate Language (CIIL). All data transmissions over the bus are ASCII encoded. The values for the command parameters can be written in integer, decimal or scientific notation. The response from the power supplies via the TLD 488-16 include CONDITIONS NOR-MAL, INVALID COMMAND and other various ERROR MESSAGES, detailed in Section III of this manual.

1-3

FIG. 1-3 TLD 488-16 CARD CAGE, MECHANICAL OUTLINE DRAWING.

## SECTION II—PREPARATION FOR USE

#### UNPACKING AND INSPECTION 2-1

- The Model TLD 488-16 and its accompanying programming card(s) have been carefully inspected and 2-2 tested prior to packing. Inspect the shipping carton(s) immediately upon receipt for evidence of damage during transit. Save the original packing material. If any indication of damage is found file a claim immediately with the responsible transport service.

- For repairs of a product damaged in shipment, contact the Kepco Factory Representative nearest you, or contact the Kepco Sales Department directly for further instruction.

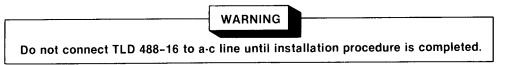

#### INSTALLATION 2.4

Set Reset Function.

The installation and set-up procedure for the TLD 488-16 consists of the following steps:

1) ON THE COMPUTER BOARD: 2) ON THE PROGRAMMING CARD(S):

Set Device Address.

Set TL 488-4A or TL 488-4B Board Address.

Set Power Supply Identification Switches.

Set Shield Ground Selector.

Install Programming Card into TLD 488-16.

3) ON THE CARD CAGE:

Set a-c line voltage.

Set PCA Connector Switches.

(For ATE power supplies only).

These steps are detailed in the following paragraphs. Refer to the fold-out Installation Drawing, FIG. 2-1 at the end of this section.

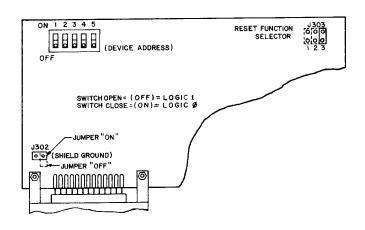

## SET DEVICE ADDRESS, RESET FUNCTION AND SHIELD GROUND SELECTOR

- The DEVICE ADDRESS for the TLD 488-16 is initially set by means of DIP switches on the COMPUTER BOARD, which occupies the bottom slot in the TLD 488-16 card cage. The DEVICE ADDRESS is the permanent LISTENER or TALKER address of the TLD 488-16 on the GPIB. It is factory pre-set to decimal "6". If a different DEVICE ADDRESS is required in your system, proceed as follow, if not go to STEP 3. There are 31 (0-30) possible choices (See Table 2-1).

- STEP 1: Place the TLD 488-16 on a bench top, its rear panel facing forward. Take off the rear panel by removing the holding screws.

- STEP 2: Carefully remove the COMPUTER BOARD from the lowest slot in the TLD 488-16, using the BOARD EJECTORS. Note that the COMPUTER board actually occupies the two bottom slots, due to its "piggy-back" construction. The four progressively higher slots are designated SLOT 1, 2, 3 and 4, with SLOT 4 being the highest in the TLD 488-16 card cage. Locate the IEEE 488 INTERFACE board with the DEVICE ADDRESS SELECTOR. This subassembly is the larger of the two "piggy-back" boards on the COMPUTER BOARD. The selector is a DIP switch, as indicated in FIG. 2-1 and detailed in FIG 2-2. The factory set device address is 6. For other choices select and set the device address according to Table 2-1.

FIG. 2-2 IEEE 488 INTERFACE BOARD ON THE COMPUTER BOARD OF THE TLD 488-16, DEVICE ADDRESS SELECTOR DETAILS.

2-1 TLD 488--06-0186

| DECIMAL<br>ADDRESS | S1-1 | S1-2 | S1-3 | S1-4 | \$1-5 |

|--------------------|------|------|------|------|-------|

| 0                  | 0    | 0    | 0    | 0    | 0     |

| 1                  | 1    | 0    | 0    | 0    | 0     |

| 2                  | 0    | 1    | 0    | 0    | 0     |

| 3                  | 1    | 1    | 0    | 0    | 0     |

| 4                  | 0    | 0    | 1    | 0    | 0     |

| 5                  | 1    | 0    | 1    | 0    | 0     |

| 6                  | 0    | 1    | 1    | 0    | 0     |

| 7                  | 1    | 1    | 1    | 0    | 0     |

| 8                  | 0    | 0    | 0    | 1 1  | 0     |

| 9                  | 1    | 0    | 0    | 1    | 0     |

| 10                 | 0    | 1    | 0    | 1    | 0     |

| 11                 | 1    | 1    | 0    | 1    | 0     |

| 12                 | 0    | 0    | 1    | 1    | 0     |

| 13                 | 1    | 0    | 1    | 1    | 0     |

| 14                 | 0    | 1    | 1    | 1    | 0     |

| 15                 | 1    | 1    | 1    | 1    | 0     |

| 16                 | 0    | 0    | 0    | 0    | 1     |

| 17                 | 1    | 0    | 0    | 0    | 1     |

| 18                 | 0    | 1    | 0    | 0    | 1     |

| 19                 | 1    | 1    | 0    | 0    | 1     |

| 20                 | 0    | 0    | 1    | 0    | 1     |

| 21                 | 1    | 0    | 1    | 0    | 1     |

| 22                 | 0    | 1    | 1    | 0    | 1     |

| 23                 | 1    | 1    | 1    | 0    | 1     |

| 24                 | 0    | 0    | 0    | 1    | 1     |

| 25                 | 1    | 0    | 0    | 1    | 1     |

| 26                 | 0    | 1    | 0    | 1    | 1     |

| 27                 | 1    | 1    | О    | 1    | 1     |

| 28                 | 0    | 0    | 1    | 1    | 1     |

| 29                 | 1    | 0    | 1    | 1    | 1     |

| 30                 | 0    | 1    | 1    | 1    | 1     |

SWITCH OFF (OPEN) = LOGIC 1 SWITCH ON (CLOSED) = LOGIC 0

TABLE 2-1 DEVICE ADDRESS SELECTION ON THE KEPCO MODEL TLD 488-16

IEEE 488 INTERFACE BOARD

TLD 488—06-0186

- STEP 3: Locate the RESET FUNCTION SELECTOR in FIG. 2-2 and place jumper into the position desired: (RESET FUNCTION should not be confused with "CIIL" op-code RST (Reset) as defined in Section III of this manual).

- POS. 1 = AUTORESET Automatically resets the system if microprocessor hangs up.

- POS. 2 = HARDWARE RESET Is activated by the IFC (Interface Clear) command (original "MATE" requirement).

- POS. 3 = Reset is activated by DCL (Device Clear) command. The factory set position is POS. 3.

- STEP 4: Locate the SHIELD GROUND SELECTOR in Fig.2-2 and place jumper in position "ON" (shields on the IEEE 488 connector connected to common) or in position "off" (shields not grounded). The factory set position is "ON".

- STEP 5: Carefully, re-insert the COMPUTER BOARD into the lowest siot (A) in the TLD 488-16, closing the BOARD EJECTORS. **NOTE:** The DEVICE ADDRESS of the TLD 488-16 serves as the LISTENER as well as the TALKER address on the IEEE bus.

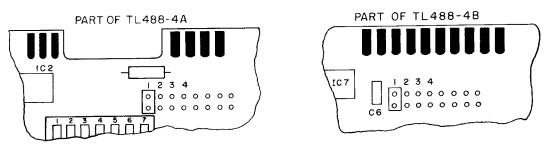

## 2-8 SET TL 488-4A or TL 488-4B BOARD ADDRESS AND POWER SUPPLY IDENTIFICATION SWITCHES.

- 2-9 The TL 488-4A or TL 488-4B Board Addresses are set by means of jumpers on the P.C. board. The board addresses permit the Controller to address from one to sixteen individual power supplies (CHANNELS 0 to 15). All TL 488 boards are shipped separate from the TLD 488-16 card cage. Before installing the board(s) into the cage, proceed as follows:

- STEP 1: Place board on a clean, cushioned surface, component side up, power supply connectors facing forward. Locate the BOARD ADDRESS SELECTOR. This selector is a jumper-type device, as indicated in FIG. 2-1 and detailed in FIG. 2-3.

FIG. 2-3 VIEW OF TL 488-4A. (LEFT) AND TL 488-4B (RIGHT) WITH BOARD ADDRESS SELECTOR DETAIL, JUMPER IN POS. 1.

- STEP 2: Place the jumper in the position equivalent to the SLOT NUMBER the board occupies in the TLD 488-16: If a single board is used (one to four power supplies are to be controlled), the board will occupy SLOT 1. Set the jumper to position 1. If several boards are used (more than four power supplies are to be controlled), the second board will occupy SLOT 2. Set the jumper to position 2 on the second board. Continue with board 3, SLOT 3, jumper to position 3 and board 4, SLOT 4, jumper to position 4.

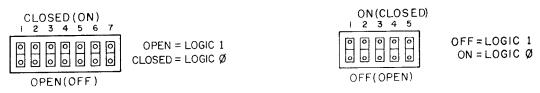

- STEP 3: Locate the POWER SUPPLY IDENTIFICATION SWITCHES as indicated in FIG. 2-1 and detailed in FIG. 2-4.

FIG. 2-4 ONE OF FOUR POWER SUPPLY IDENTIFICATION SWITCHES ON THE TL 488-4A BOARD (LEFT) AND ON THE TL 488-4B BOARD (RIGHT).

STEP 4: Find the power supply model to be controlled at CHANNEL 0 in the Table 2-2 or Table 2-3 and set the switch positions as indicated in the table. Continue with the power supply occupying CHANNEL 1 and so on, until all power supply identification switches are set. Set switches for unoccupied channels as directed in Table 2-2 or Table 2-3.

**NOTE:** There are seven (7) switch positions for ATE power supplies as shown in Table 2-2. Switch position 7 (S1-7) serves to select SLOW or FAST operating modes. For BOP power supplies only five (5) positions are provided as shown in Table 2-3.

STEP 5: Install the TL 488-4A or TL 488-4B board(s) into the appropriate slot in the TLD 488-16 card cage. Replace the rear panel of the TLD 488-16 and fasten with the panel holding screws.

| MODEL                     | SW<br>#1        | SW<br>#2          | SWITO<br>SW<br>#3 | CHES<br>SW<br>#4  | SW<br>#5      | SW<br>#6      | (SWITCH # 7<br>CLOSED) | MONITOR<br>TIME OUT <sup>(1)</sup> | (SWITCH #7<br>OPEN) | MONITOR<br>TIME OUT <sup>(1)</sup> |

|---------------------------|-----------------|-------------------|-------------------|-------------------|---------------|---------------|------------------------|------------------------------------|---------------------|------------------------------------|

| ATE 6-5M                  | _ <del>#'</del> | 0                 | 0                 | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

|                           | 1               | 0                 |                   | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 05 OM                 | 0               | 1                 | 0                 | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 25-2M                 |                 | <del>'</del>      | 0                 | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 55 1M                 | 1               | 0                 | 1                 | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 35 0.7M               | 0               | 0                 | <u>'</u>          | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 100, 0.5M             | 0               | <del></del> 1     | <u>'</u>          | 0                 | 0             |               | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 100-0.5M              | 1               | <u>'_</u><br>1    | <u>'</u>          | 0                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 150-0.3M<br>ATE 6-10M | 0               | <del>'</del> _    | <del>.</del>      | 1                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

|                           | 1               | 0                 | 0                 | <del>.</del>      | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 15-6M<br>ATE 25-4M    | 0               | 1                 | 0                 | <del>'</del> _    | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

|                           | 1               | <del>'</del>      | 0                 | 1                 |               | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 55 3M                 | 0               | 0                 | 1                 | 1                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 55-2M                 | 1               | 0                 | <u>'</u>          | 1                 | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millisec                        |

| ATE 75-1.5M<br>ATE 100-1M | 0               | 1                 | 1                 | 1                 | 0             |               | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millised                        |

|                           | 1               | <u>'</u> _<br>1   | <u>'</u><br>1     | <u>'</u>          | 0             | 0             | SLOW MODE              | 2.5 sec                            | FAST MODE           | 50 millised                        |

| ATE 6. 25M                | 0               | 0                 | 0                 | 0                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 6-25M<br>ATE 15-15M   | 1               | 0                 | 0                 | 0                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 25-10M                | 0               | 1                 | 0                 | 0                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 36-8M                 | 1               | <u>'</u>          | 0                 | 0                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 55-5M                 | 0               | 0                 | 1                 |                   | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 75-3M                 | 1               | 0                 | <del>'</del>      | 0                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 100-2.5M              | 0               | 1                 | <u>'</u><br>1     | 0                 | <u>·</u>      | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 150-1.5M              | 1               | <u>'</u> _        | <del>'</del>      | 0                 | <u>.</u><br>1 | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 325-0.8M              | 1               | <del>'</del>      | 0                 | 1                 | 0             | <del></del>   | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 6-50M                 | 0               | 0                 | 0                 | <u>-</u>          | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 0-30W                 | 1               | 0                 |                   | <u>·</u> _        | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 25-20M                | 0               | 1                 | 0                 | 1                 | <u>;</u><br>1 | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 36-15M                | 1               | <u>'</u> _        |                   | 1                 | 1             | 0             | SLOW MODE              | 10 sec                             | FAST MODE           | 50 millised                        |

| ATE 55-10M                | 0               | <del>_</del>      | 1                 | <u>·</u> _<br>1   | 1             | 0             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| ATE 75-8M                 | 1               | 0                 | <u>-</u>          | 1                 | 1             | 0             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| ATE 100-5M                | 0               | 1                 | <u>·</u>          | <del>.</del><br>1 | 1             | 0             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| ATE 150-3.5M              | 1               | <u>'</u> -<br>1   | <u>·</u><br>1     | <u>:</u><br>1     | 1             | 0             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| ATE 6-100M                | 0               | 0                 | <u>'</u> _        | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| 21333                     | 0               | 0                 | 0                 | 1                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millised                        |

| ATE 15-50M                | 1               | 0                 | 0                 | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 25-40M                | 0               | 1                 | 0                 | 0                 | 0             | <u>-</u><br>1 | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 36-30M                | 1               | <del>.</del><br>1 | 0                 | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 55-20M                | 0               | <u>'</u>          | 1                 | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 55-20M<br>ATE 75-15M  | 1               | 0                 | <u>'</u> _<br>1   | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 100-10M               | 0               |                   | 1                 | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| ATE 150-7M                | 1               | 1                 | <u>·</u><br>1     | 0                 | 0             | 1             | SLOW MODE              |                                    | FAST MODE           | 50 millise                         |

| NO SUPPLY                 | 1               | <u>'</u><br>1     | <u>_</u>          |                   | <del>_</del>  | 1             | X                      | N.A.                               | X                   | N.A.                               |

TABLE 2-2 MODEL TABLE FOR SETTING THE POWER SUPPLY IDENTIFICATION SWITCHES ON TL 488-4A NOTE: 0 = CLOSED (ON), 1 = OPEN (OFF), X = DON'T CARE, N.A. = NOT APPLICABLE

<sup>(1)</sup> Monitor time outs are time delays, imposed by the TLD 488-16 to allow the power supply output to settle after a change in output value has been commanded.

|              |          | SWIT     |          |          |          |                                    |

|--------------|----------|----------|----------|----------|----------|------------------------------------|

| MODEL        | SW<br>#1 | SW<br>#2 | SW<br>#3 | SW<br>#4 | SW<br>#5 | MONITOR<br>TIME OUT <sup>(1)</sup> |

| BOP 50-2M    | 0        | 0        | 0        | 0        | 0        | 50 millisec.                       |

| BOP 100-1M   | 1        | 0        | 0        | 0        | 0        | 50 millisec.                       |

| BOP 20-10M   | 0        | 1        | 0        | 0        | 0        | 50 millisec.                       |

| BOP 36-6M    | 1        | 1        | 0        | 0        | 0        | 50 millisec.                       |

| BOP 50-4M    | 0        | 0        | 1        | 0        | 0        | 50 millisec.                       |

| BOP 72-3M    | 1        | 0        | 1        | 0        | 0        | 50 millisec.                       |

| BOP 100-2M   | 0        | 1        | 1        | 0        | 0        | 50 millisec.                       |

| BOP 20-20M   | 1        | 1        | 1        | 0        | 0        | 50 millisec.                       |

| BOP 36-12M   | 0        | 0        | 0        | 1        | 0        | 50 millisec.                       |

| BOP 50-8M    | 1        | 0        | 0        | 1        | 0        | 50 millisec.                       |

| BOP 72-6M    | 0        | 1        | 0        | 1        | 0        | 50 millisec.                       |

| BOP 100-4M   | 1        | 1        | 0        | 1        | 0        | 50 millisec.                       |

| BOP 200-0.5M | 0        | 0        | 1        | 1        | 0        | 50 millisec.                       |

| BOP 200-1M   | 1        | 0        | 1        | 1        | 0        | 50 millisec.                       |

| NO SUPPLY    | 11       | 1        | 1        | 1        | _ 1      | N.A.                               |

TABLE 2-3 MODEL TABLE FOR SETTING THE POWER SUPPLY IDENTIFICATION SWITCHES ON TL 488-4B NOTE: 0 = ON (CLOSED), 1 = OFF (OPEN).

<sup>(1)</sup> Monitor time outs are time delays, imposed by the TLD 488–16 to allow the power supply output to settle after a change in output value has been commanded.

#### 2-10 SET A-C LINE VOLTAGE

**NOTE:** The TLD 488-16 is normally connected for operation on 105-125V a-c lines. If operation on 210-250V a-c lines is desired, proceed as follows:

- STEP 1: With the a-c power cord removed from the FUSED MULTIVOLTAGE CONNECTOR, lift-up the transparent cover and lift the FUSE-PULL lever up. Remove fuse and put aside.

- STEP 2: Remove the miniature SELECTOR CARD, turn so that the desired a-c input voltage is visible and replace card, pushing it firmly into the slot.

- STEP 3: Reinstall fuse. **NOTE:** The same value fuse is used (5A-250V, KEPCO P/N 141-0056 or BUSS MDA-5) for operation on 115V a-c or on 230V a-c. Close cover and insert the a-c power cord into the connector.

## 2-11 INSTALLATION OF THE MODEL TLD 488-16 (Refer to FIG. 2-5)

2-12 The TLD 488–16 may be operated on the bench or it can be installed into a standard 19 inch equipment rack. The sides of the unit have inserts for chassis slide mounting. Chassis slides must be drilled according to the mounting hole pattern in FIG. 2-5 and must not obstruct the ventilation slots. A suitable slide is Jonathan Series 130-QD or equivalent.

FIG. 2-5 INSTALLATION DRAWING, MODEL TLD 488-16.

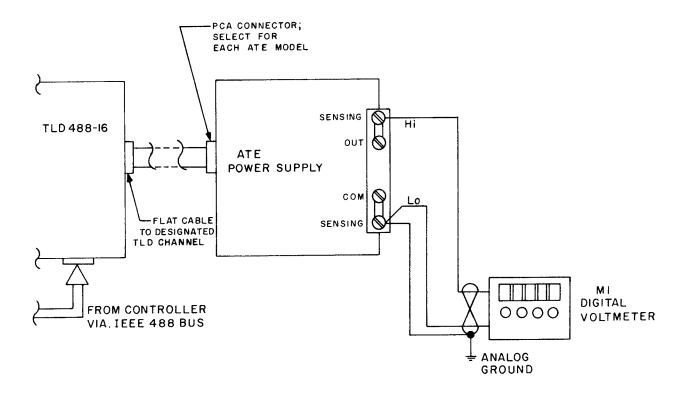

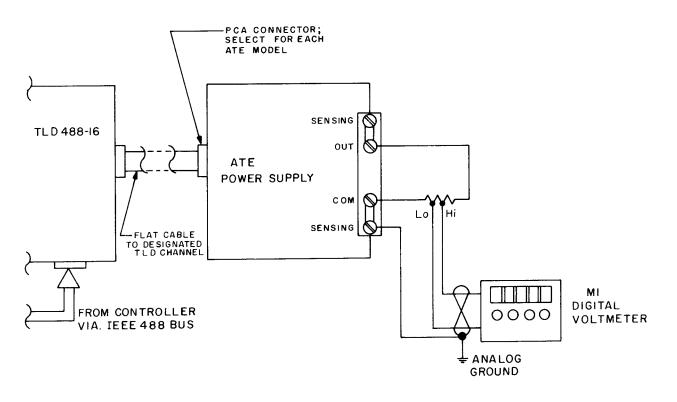

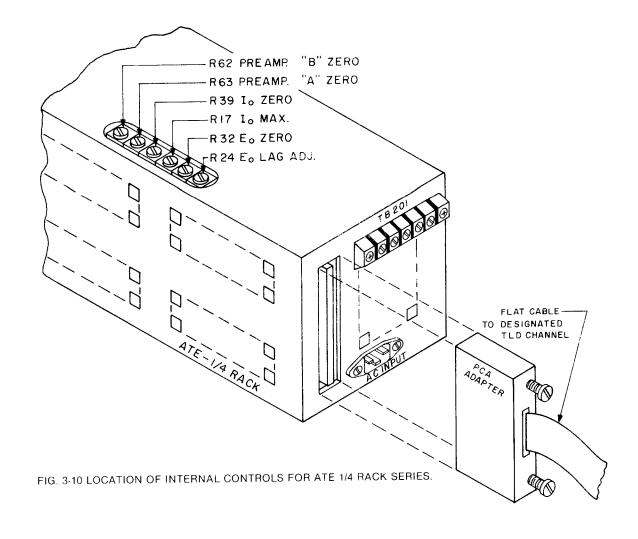

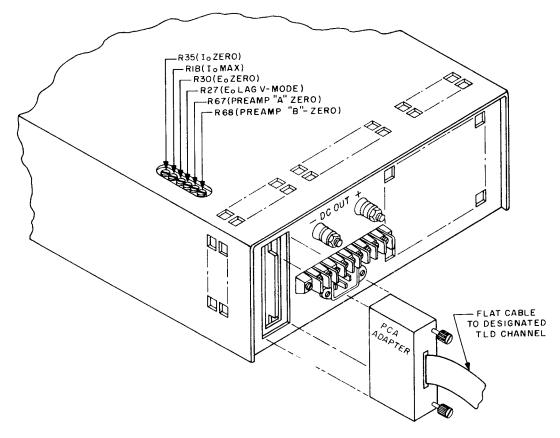

# 2-13 PREPARATION AND INSTALLATION OF THE KEPCO SERIES PCA CABLE ASSEMBLIES. (ATE POWER SUPPLIES WITH TL 488-4A CARDS ONLY).

2-14 The PCA cable assembly connects each ATE power supply to its pre-selected output channel on the TLD 488-16. Each PCA cable assembly is selected for the particular power supply (Refer to Section I, paragraph 1-6) and in addition must be set for selection of the operating mode (Slow or Fast) and for overvoltage protection (Tracking or Non-Tracking). Proceed as follows:

STEP 1: Remove the flat cable from the connector assembly by opening the EJECTOR LATCH at the large connector end. Take the large connector, remove the two (2) 4-40 holding screws and take out the connector insert. Refer to FIG. 2-6.

FIG. 2-6 PCA CABLE ASSEMBLY AND POWER SUPPLY CONNECTOR INSERT DETAIL, TOP VIEW.

NOTE: PCA-2 Series Connectors have a single jumper only (J1).

STEP 2: Determine the design group of the power supplies to be programmed. For power supplies in the ATE 1/4 RACK SERIES enter Table 2-4. For models in the ATE 1/2, 3/4 and FULL RACK SERIES enter Table 2-5. Place the jumper(s) and set the switches as directed in the tables.

STEP 3: Re-install the connector insert into the connector shell, re-attach the cable (note key-way) and mount the PCA connector assembly onto the power supply. Connect the other end of the PCA to the designated output channel on the TLD 488-16.

| <u> </u> | SLO               | <br>ow   | FAST            |          |  |  |

|----------|-------------------|----------|-----------------|----------|--|--|

| SWITCH   |                   | OVERVO   | DLTAGE          |          |  |  |

| #        | NON<br>TRACKING   | TRACKING | NON<br>TRACKING | TRACKING |  |  |

| S1       | ON <sup>(1)</sup> | ON       | OFF             | OFF      |  |  |

| S2       | OFF(2)            | OFF      | ON              | ON       |  |  |

| S3       | OFF               | OFF      | ON              | ON       |  |  |

| S4       | ON                | OFF      | ON              | OFF      |  |  |

| S5       | OFF               | ON       | OFF             | OFF      |  |  |

| S6       | OFF               | OFF      | OFF             | ON       |  |  |

| S7       | OFF               | ON       | OFF             | OFF      |  |  |

| S8       | ON                | OFF      | ON              | ON       |  |  |

$<sup>^{(1)}</sup>$  ON = CLOSED

|        | SLO                | OW       | FAST            |          |  |  |  |  |

|--------|--------------------|----------|-----------------|----------|--|--|--|--|

| SWITCH | OVERVOLTAGE        |          |                 |          |  |  |  |  |

| #      | NON<br>TRACKING    | TRACKING | NON<br>TRACKING | TRACKING |  |  |  |  |

| S1     | Not Used           | Not Used | Not Used        | Not Used |  |  |  |  |

| S2     | OFF <sup>(1)</sup> | OFF      | ON              | ON       |  |  |  |  |

| S3     | OFF(2)             | OFF      | ON              | ON       |  |  |  |  |

| S4     | ON                 | OFF      | ON              | OFF      |  |  |  |  |

| S5     | OFF                | ON       | OFF             | OFF      |  |  |  |  |

| S6     | OFF                | OFF      | OFF             | ON       |  |  |  |  |

| S7     | OFF                | ON       | OFF             | OFF      |  |  |  |  |

|        | ON                 | OFF      | ON              | ON       |  |  |  |  |

<sup>(1)</sup> ON = CLOSED

| JUMPER # | SLOW | FAST |

|----------|------|------|

| J1       | IN   | OUT  |

| J2       | IN   | OUT  |

TABLE 2-4 SWITCH AND JUMPER SELECTION ON THE PCA-1 CONNECTOR ASSEMBLY FOR QUARTER RACK ATE POWER SUPPLIES.

| FAST |

|------|

|      |

| OUT  |

|      |

TABLE 2-5 SWITCH AND JUMPER SELECTION ON THE PCA-2 CONNECTOR ASSEMBLY FOR ½, ¾ AND FULL RACK ATE POWER SUPPLIES.

<sup>(2)</sup> OFF = OPEN

<sup>(2)</sup> OFF = OPEN

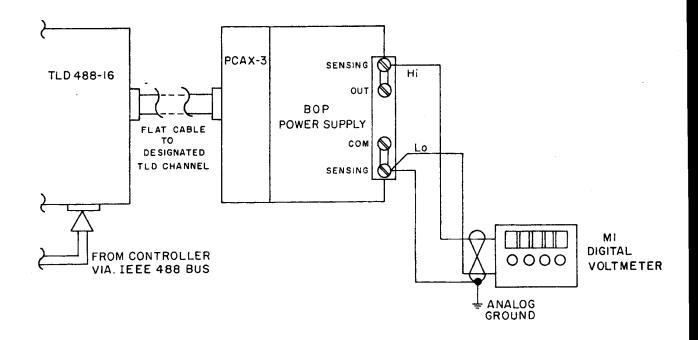

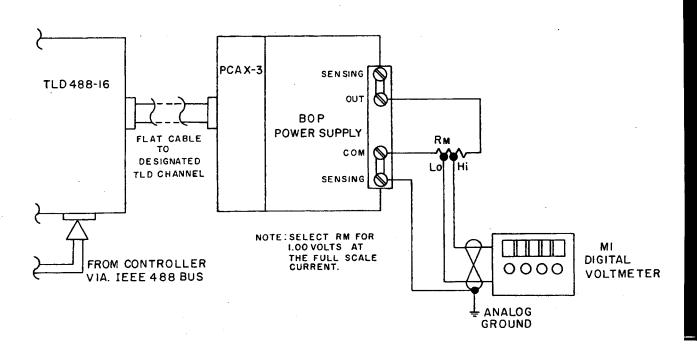

- 2-15 INSTALLATION OF PCA X-3 AND CABLE (BOP POWER SUPPLIES) WITH TL 488-4B CARDS.

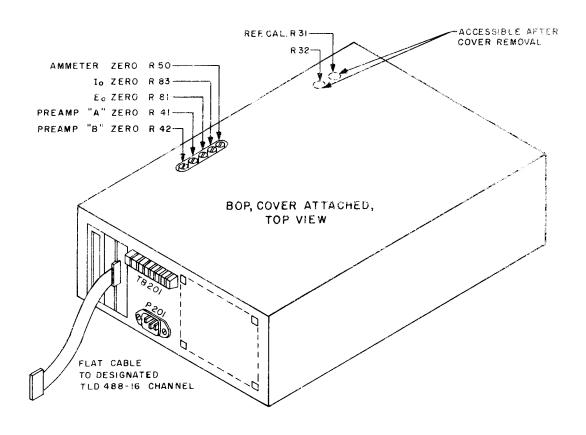

- 2-16 For BOP power supplies, the interface between the BOP and the TLD 488–16 programmer consists of the Model PCA X-3 interface card and a set of three (3) cables with connectors. The Model PCA X-3 interface card is installed inside the BOP as shown in FIG. 2-7. Detailed installation instructions are provided with the PCA X-3 Instruction Manual.

FIG. 2-7 BOP TOP VIEW (SIMPLIFIED) WITH PCA X-3 INTERFACE INSTALLED.

- 2-17 Once the PCA X-3 is installed in the predetermined space on the BOP chassis, the cables may be connected as follows:

- 1) CABLE (1), 15 wires, from PCA X-3, P2 to BOP-A1-P5

- 2) CABLE (2), 5 wires, from PCA X-3, P1 to BOP-A1-P6

- 3) (3), 20 wires, from PCA X-3, J1 to TL 488-4B board installed in the TLD 488-16 Programmer, SLOT number and CHANNEL number depending on position of board in the TLD.

## 2-18 FINAL SYSTEM INTERCONNECTIONS.

2-19 Connect the TLD 488-16 to the GPIB, connect the STATUS MONITOR INTERFACE to the SYSTEM CONTROLLER and make the remaining connections from the power supply outputs to the loads, either directly, or via the ISOLATION RELAYS. Mating connectors for the relay interface, as well as for the status monitor interface are provided with the TLD 488-16. The installation of the TLD 488-16 system is now complete. System Calibration is described in Section III, paragraphs 3-51 through 3-56.

2-8

FIG. 2-8 MODEL TLD 488-16, REAR TERMINATIONS.

#### 2-20 REAR TERMINATIONS ON THE TLD 488-16.

- A) A–C input. The power line connection is made via a removable a-c power cord, KEPCO P/N 118-0552 (supplied). TLD 488–16 is delivered for operation on a nominal 115V a-c, single phase line. For operation on 230V a-c, see paragraph 2-10.

- B) POWER SUPPLY I/O PORTS. These ports are terminated with connectors each of which accept a Kepco Series PCA cable assembly for ATE power supplies (see FIG. 2-6) or a 20-wire flat cable for BOP power supplies (see FIG. 2-7).

|                                                                                                     | ATE I/O PORT<br>TERMINATIONS (14-WIRE CABLE)                                                                                                                                                                  |                                                                                                                | BOP I/O PORT<br>TERMINATIONS (20-WIRE CABLE)                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN 1<br>PIN 2<br>PIN 3<br>PIN 4,5<br>PIN 6,7,8,9<br>PIN 10<br>PIN 11<br>PIN 12<br>PIN 13<br>PIN 14 | MODE FLAG CROWBAR FLAG DEVICE PRESENT FLAG COMMON (INPUT) NO CONNECTION VOLTAGE OUTPUT (0-10V d-c) P.S. VOLTAGE MONITOR (0-10V d-c) COMMON (OUTPUT) P.S. CURRENT MONITOR (0-1V d-c) CURRENT OUTPUT (0-1V d-c) | PIN 1 PIN 2 PIN 3 PIN 4,5 PIN 6,7,8,9 PIN 10 PIN 11 PIN 12 PIN 13 PIN 14 PIN 15 PIN 16,17 PIN 18 PIN 19 PIN 20 | OVERLOAD FLAG TURN-OFF FLAG DEVICE PRESENT FLAG COMMON (INPUT) NO CONNECTION MAIN CHANNEL OUTPUT (0 to ± 10V d-c) P.S. VOLTAGE MONITOR (0 to ± 10V d-c) COMMON (OUTPUT) P.S. CURRENT MONITOR (0 to ± 10V d-c) LIMIT CHANNEL OUTPUT (0 to + 10V d-c) MODE (V/Ī) COMMON (OV), REMOTE + 5V d-c + 15V d-c - 15V d-c |

#### NOTES:

- 1) The INPUT COMMON and the OUTPUT COMMON are optically isolated from each other for 500V d-c.

- 2) SIGNALS at pins 1,2 and 3 are with reference to COMMON (Input), Pin 4. All other signals are with reference to COMMON (Output) pin 12.

- C) STATUS MONITOR PORT. This port is terminated with a miniature, 2 pin locking-type connector, KEPCO P/N 143-0313 (supplied). The function of the status monitor lines is described in Section III, paragraph 3-34.

- D) IEEE 488 BUS (GPIB) I/O PORT. This port is terminated with a 24 pin IEEE 488 connector and conforms mechanically and electrically to the IEEE 488 standard. Note that the TLD 488-16 has a Shield Ground selector on the IEEE 488 Interface board, providing the option of either grounding the shields externally or internally. Refer to Section II, FIG. 2-2 and paragraph 2-7, Step 4.

- E) AUXILIARY D-C POWER. A stabilized auxiliary d-c voltage source (+5V at 10A) is available at the rear panel. It is terminated with a two-terminal outlet, with the mating connector (Kepco P/N 142-0245) supplied.

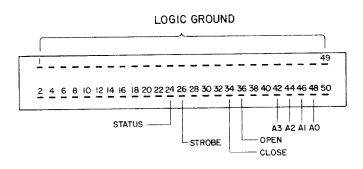

F) I/O ISOLATION RELAY PORT. This port is terminated with a 50-pin standard PC board connector (0.100 spacing, for 1/16 thick board, KEPCO P/N 143-0321).

FIG. 2-9 RELAY PORT, PIN-OUTS

The line designations are as follows:

$A_0$  J1-48 Address lines, logic high = true  $A_1$  J1-46

A<sub>2</sub> J1-44

A<sub>3</sub> J1-42

Strobe (Strobe) J1-26, logic low = true

Open J1-36, logic high = true

Close J1-34, logic high = true

Status (open) J1-24 logic low = relay open

#### NOTE:

For applications where the optional external ISOLATION RELAYS are not used, a jumper connection between Pin 24 (RELAY STATUS) and Pin 23 (LOGIC GROUND) at the I/O ISOLATION PORT CONNECTOR will eliminate unnecessary initial error messages related to the ISOLATION RELAYS. In the absence of the jumper (Status Line HIGH — means Relay Closed) and with the default state R1 at POWER ON (ENABLE STATUS ERROR MESSAGES) a number of error messages such as "RELAY NOT OPEN" will be generated equal to the number of power supplies connected to TLD 488-16.

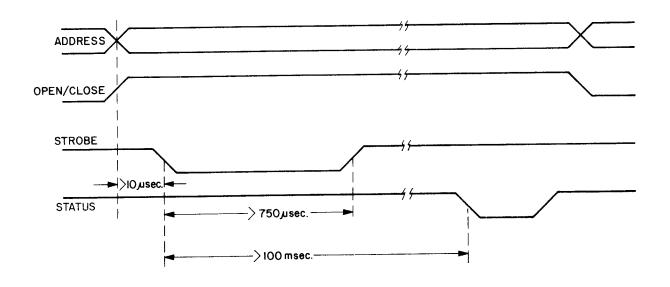

FIG. 2-10 TIMING DIAGRAM, I/O ISOLATION RELAY PORT

## **SECTION III—OPERATION**

#### 3-1 GENERAL

Once the TLD 488–16 INTERACTIVE PROGRAMMER (TLD) has been prepared and interconnected as described in Section II of this manual, operation can proceed. The TLD functions as a TALKER/LISTENER on the GENERAL PURPOSE INTERFACE BUS (GPIB, defined by IEEE Standard 488 and IEC625-1). The GPIB CONTROLLER will communicate with the TLD via the GPIB, using the specified IEEE 488 protocol as well as elements of the CONTROL INTERFACE INTERMEDIATE LANGUAGE (CIIL). Since the TLD can accommodate from one (1) to sixteen (16) programmable power supplies, up to sixteen power supplies may be digitally programmed via the GPIB. The CONTROLLER may be programmed to implement the MODULAR AUTOMATIC TEST EQUIPMENT (MATE) protocol<sup>(1)</sup>, or it may be programmed for non-MATE applications. For non-MATE applications, the CONTROLLER should have the capability to implement the SERVICE REQUEST and SERIAL-POLL functions.

#### 3-3 COMMUNICATIONS

- 3-4 INTERNAL. All internal communications within the TLD 488-16 take place via the Intel Multibus™, directed by a program residing in PROM memory.

- 3-5 EXTERNAL. Communications between the TLD 488-16 TALKER/LISTENER and the computer, functioning as a CONTROLLER/TALKER/LISTENER take place according to the IEEE 488 protocol. The TLD 488-16 implements the interface functions listed in Table 3-1.

- (1) Refer to PROPOSED MATE SYSTEM CONTROL INTERFACE STANDARD, No. 2806763, Rev. B, 25 September 1983 or later.

| GPIB FUNCTION      | SUBSET SYMBOL | COMMENTS                                    |

|--------------------|---------------|---------------------------------------------|

| Source Handshake   | SH1           | Complete Capability                         |

| Acceptor Handshake | AH1           | Complete Capability                         |

| Talker             | Т6            | Basic talker, serial poll, unaddress if MLA |

| Listener           | L4            | Basic listener, unaddress if MTA            |

| Service Request    | SR1           | Complete Capability                         |

| Remote Local       | RL0           | No Capability                               |

| Parallel Poll      | PP0           | No Capability                               |

| Device Clear       | DC1           | Complete Capability                         |

| Device Trigger     | DT0           | No Capability                               |

| Controller         | C0            | No Capability                               |

TABLE 3-1 INTERFACE FUNCTIONS IMPLEMENTED BY TLD 488-16

A) In COMMAND MODE, the TLD 488-16 will send or receive remote messages per IEEE 488 protocol as listed in Table 3-2.

| MNEMONIC | MESSAGE DESCRIPTION   | COMMENTS         |  |  |

|----------|-----------------------|------------------|--|--|

| ATN      | Attention             | Received         |  |  |

| DAC      | Data Accepted         | Received or Sent |  |  |

| DAV      | Data Valid            | Received or Sent |  |  |

| DCL      | Device Clear          | Received         |  |  |

| IFC      | Interface Clear       | Received         |  |  |

| MLA      | My Listen Address     | Received         |  |  |

| MTA      | My Talk Address       | Received         |  |  |

| OTA      | Other Talk Address    | Received         |  |  |

| RED      | Ready for Data        | Received or Sent |  |  |

| SDC      | Selected Device Clear | Received         |  |  |

| SPD      | Serial Poll Disable   | Received         |  |  |

| SPE      | Serial Poll Enable    | Received         |  |  |

| SRQ      | Service Request       | Sent             |  |  |

| UNL      | Unlisten              | Received         |  |  |

| UNT      | Untalk                | Received         |  |  |

TABLE 3-2 MESSAGES SENT OR RECEIVED BY THE TLD 488-16 IN COMMAND MODE.

B) In DATA MODE, the TLD 488-16 will send or receive remote messages per IEEE 488 protocol as listed in Table 3-3. These messages are enabled during the "handshake" cycle, with the TLD 488-16 operating as a TALKER or as a LISTENER.

| MNEMONIC | MESSAGE DESCRIPTION       | COMMENTS         |

|----------|---------------------------|------------------|

| DAB      | Data Byte                 | Received or Sent |

| END      | End                       | Received or Sent |

| EOS      | End of String (line feed) | Received or Sent |

| RQS      | Request Service           | Sent             |

| STB      | Status Byte               | Sent             |

TABLE 3-3 MESSAGES SENT OR RECEIVED BY THE TLD 488-16 IN DATA MODE.

#### 3-6 CIIL CODES

3-7 All other communication on the GPIB bus in DATA MODE are not defined by the IEEE 488 Standard. Instead, the syntax and mnemonics of the Control Interface Intermediate Language (CIIL)<sup>(1)</sup> are used to program the power supplies, test and report their status and send error messages. The CIIL elements used for these purposes are the OPERATION CODES, NOUNS and NOUN MODIFIERS listed below and discussed in detail in the following paragraphs.

(1) CIIL is a subset of ATLAS. For special or non-MATE requirements some non-CIIL commands are accepted. Refer to paragraphs 3-38 and 3-39.

| A) | CIIL OPERATION ( | CODES (OP CODES):     |

|----|------------------|-----------------------|

|    | FNC              | Function              |

|    | SET              | Setup                 |

|    | SRX              | Set Maximum           |

|    | SRN              | Set Minimum           |

|    | CLS              | Close                 |

|    | OPN              | Open                  |

|    | RST              | Reset                 |

|    | CNF              | Confidence Test       |

|    |                  | Internal Self-Test    |

|    |                  | Status                |

| B) | NOUNS:           |                       |

| •  | DCS              | Direct Current Source |

| C) | NOUN MODIFIERS:  |                       |

| -, | VOLT             | Voltage               |

|    |                  | Voltage Limit         |

|    |                  | Current               |

|    |                  | Current Limit         |

- D) DELIMITERS: All OP CODES and OPERANDS must be separated by the ASCII "space" code (SP)

- E) TERMINATORS: The MATE (Modular Automatic Test Equipment) protocol requires that all command strings are terminated by a "carriage return" and a "line feed" (cr) (lf). Alternately, for non-MATE applications, the END message (See Table 3-3) may be utilized as a terminator. The TLD 488–16 sends both, a "line feed" (lf) and the END command when messages are sent. It accepts both, "line feed" (lf) and the END command as terminators when receiving messages.

- F) TIME-OUTS: (To obtain a valid status indication):

- 1) The required delay times following a SET command string are listed in Section II, Tables 2-2 and 2-3.

- 2) The required delay time following an "open" (OPN) or a "close" (CLS) command is 100 milliseconds.

- 3) The required delay time following the Confidence Test (CNF) or Internal Self Test (IST) command is 15 seconds.

#### 3-8 THE FUNCTION COMMAND.

3.9 FNC — Function Op Code. This operator is uniquely associated with the start of a set-up sequence for the device. There are two (2) operand fields associated with this op code.

| OP CODE |     |    | OPERAND 1 | OPERAND 2 |       |  |

|---------|-----|----|-----------|-----------|-------|--|

| SYNTAX: | FNC | SP | DCS       | SP        | :CHnn |  |

NOTE: Incomplete command. Complete Commands are followed by SET command and terminated with the ASCII characters "cr" (carriage return) and "If" (line feed).

- A) The Function Command is always the first command in the set-up sequence.

- B) The first operand field of the command contains the three (3) letter mnemonic pertaining to the device on the GPIB bus. For the Kepco Model TLD 488-16 it is "DCS" (Direct Current Source). **NOTE:** An ASCII "space" (SP), ASCII 32 is used as a delimiter between OP CODE and OPERAND and between OPERANDS.

- C) The second operand field of the command is used to select the specific input "Port" of the device being programmed. Since the Kepco Model TLD 488–16 has sixteen possible power supplies connected to it, the "nn" in Operand 2 is a one to two digit ASCII integer (0 to 15), designating the power supply being programmed at this time.

#### 3-10 THE SET, SRX and SRN COMMANDS.

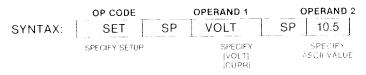

3-11 SET — Setup Op Code. This operator is used to specify the output mode of the power supply being programmed. The NOUN MODIFIER as the first operand specifies the chosen output mode and the second operand specifies the value in ASCII characters.

NOTE: Incomplete command. Complete Commands are preceded by FNC command and terminated with the ASCII characters "cr" (carriage return) and "lf" (line feed).

A) The first operand field of the command contains the four (4) letter mnemonic for the output mode of the power supply. The choices are:

VOLT — Voltage Mode Operation CURR — Current Mode Operation

VLTL — Voltage Limit Operation CURL — Current Limit Mode Operation

B) The second operand field of the command contains the value assigned to the chosen output mode. This value may be specified as accurate as the resolution of the TLD 488-16 allows (12 bits, or VALUE ÷ 4095). It can be specified directly in ASCII integer, decimal, or in scientific notation.

**NOTE:** There are two (2) SET commands, separated by the ASCII "space" delimiter, for each power supply being programmed. The following combinations of NOUN MODIFIERS can **not** be used together in the SET sequence for a single power supply:

VOLTwithCURRVLTLwithCURLThe only correct combinations are:VOLTwithCURL orVOLTwithVLTLCURRwithVLTLCURRwithCURL

- C) For unipolar power supplies (Kepco Series ATE), polarity signs (+ or -) preceding the voltage or current values in OPERAND 2 are optional. For bipolar power supplies (Kepco Series BOP), polarity signs must be used with OPERAND 2 to determine the polarity of their output terminal with reference to their common terminal.

- D) In addition to the SET Command, two (2) related Op Codes may be used to specify the maximum and minimum values for the four (4) NOUN MODIFIERS VOLT, CURR, CURL and VLTL:

- 1) SRX Set Maximum

- 2) SRN Set Minimum

The format of the command sequence is identical to that used for the SET Command, with SRX and SRN replacing SET in the syntax. SRX and SRN may be used previous to SET in the complete command sequence sent to a single power supply channel. (refer to paragraph 3-24) to establish the desired operating range of each of the four (4) Noun Modifiers. If the subsequent SET Command exceeds the limits established by SRX and SRN, an error message will result (see paragraph 3-32).

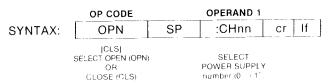

#### 3-12 THE OPEN/CLOSE RELAY COMMANDS

3-13 An external (optional) relay is interposed between the output terminals of each of the power supplies and the associated load or the (optional) switching systems. The relay is under the control of the Kepco Model TLD 488-16 via a separate, discrete interface and responds as follows:

**NOTE:** All complete Commands are terminated with the ASCII characters "cr" (carriage return) and "If" (line feed).

- A) OPN—Open Op Code. This operator is used to open the external relay associated with the power supply specified by the operand. Only a single operand is used with this op code. It is identical in format and meaning to the port identification field of the FNC command.

- B) CLS—Close Op Code. This operator is analogous to the OPN op code, except that the TLD 488-16 closes the external relay associated with the power supply specified by the operand.

#### 3-14 THE RST (RESET) COMMAND

3-15 RST — Reset Op Code. This operator is used to program the addressed power supply output to zero and open the external relay.

|         | OP CODE |  | OPERAND 1 |    | OPERAND 2 |       |  |

|---------|---------|--|-----------|----|-----------|-------|--|

| SYNTAX: | RST SP  |  | DCS       | SP | :CHnn     | cr If |  |

The RST command has the same operand fields as the FNC command.

#### 3-16 THE CONFIDENCE TEST COMMAND

3-17 CNF — Confidence Test Op-Code. This operator commands the TLD 488-16 to execute the confidence test procedure defined for the power supplies controlled by it. As a result of the CNF (Confidence Test) Command, all isolation relays are opened and an internal, localized test is performed. This test ascertains if all the function blocks of the control section (microcomputer) are working properly. Also, the CNF command programs all the power supplies connected at the I/O ports to their maximum ratings and then checks for the error flags. Upon completion of the test, all ports of the TLD 488-16 remain isolated (Relays Open), while the power supply outputs are programmed to zero.

No operators are associated with this op-code. The result of the confidence test is reported in response to the status (STA) command. The "STA" command should be issued only after the required delay time (15 sec.) is observed.

#### 3-18 INTERNAL SELF-TEST COMMAND

3-19 IST — Internal Self-Test Op Code. This operator evokes the identical response as the CNF command, since TLD 488-16 is not designed to support an internal self-test (BIT).

### 3-20 STATUS COMMAND

3-21 STA — Status Request Op Code. This operator commands the TLD 488-16 to report its current operating status.

There are no operands associated with this operator. The response for the status request is in accordance with the Response Message Syntax described in paragraph 3-27. It is important to impose the proper time delays (See paragraph 3-27) before the status command (STA) is given. The TLD 488–16 responds to the status request as soon as it is talk-addressed by the controller. If conditions are normal, only one response message is sent (see paragraph 3-27). If conditions are abnormal, the controller (Test Executive) should send multiple status commands and talk addresses to the TLD 488–16 until all error messages are collected and transmitted.

#### 3-22 ERROR HANDLING COMMANDS

3-23 TO — Erase Error Message Op Code. This operator commands the TLD 488-16 to erase previously recorded, unreported non-catastrophic error messages from the error buffer as soon as a new valid command is received or a catasthrophic error occurs. This is the default state after power-on.

T1 — Do Not Erase Error Message Op Code. This operator commands the TLD 488–16 **not** to erase previously recorded, unreported error messages from the error buffer. Error messages may be retrieved from the error buffer one by one for each STA command received. In order to gather all error messages, multiple STA commands and TALK ADDRESSES should be sent by the controller. The error buffer is clear of error messages if the response for the STA command is a "normal" response message (space, cr, lf).

| OP CODE |    |    |    |  |  |  |  |  |

|---------|----|----|----|--|--|--|--|--|

| SYNTAX: | Т0 | cr | lf |  |  |  |  |  |

| or      | T1 | cr | lf |  |  |  |  |  |

#### 3-24 BUS TRANSMISSION FORMAT.

3-25 The CIIL transmission format for a single power supply channel are given here as an example. The example given will address the power supply, set the output voltage and the current limit, check the status and subsequently reset all parameters to zero:

**NOTE:** Each complete command is terminated with the ASCII carriage return (cf) and the ASCII line feed (lf) character.

| SET: | FNO          | SP  | DC | S   | S  | P | :0 | )<br>} | 10  | SP  |    |    |

|------|--------------|-----|----|-----|----|---|----|--------|-----|-----|----|----|

|      | SET          | SP  | VC | L   | Γ  | S | Р  | 1      | 0   | SP  |    |    |

|      | SEI          | SP  | CL | IRI | _  | S | Р  | 2      | 2.5 | cr  | If |    |

| STAT | US C         | HEC | K: | 5   | ST | Α | С  | r      | lf  |     |    |    |

| RESE | <b>T</b> : F | RST | SP | [   | С  | S | S  | Р      | :(  | СНО | cr | if |

3-26 Note that the individual CIIL statements for the SET command are shown on three separate lines for readability only. In actuality, they must be concatenated into a single ASCII string, with blank delimiters separating the statements.

#### 3-27 RESPONSE MESSAGE SYNTAX

- 3-28 The Controller (Test Executive) requests the present operating Status (via the STA command and the TALKER ADDRESS) of the TLD 488-16. In order to obtain a meaningful response, the controller should use the STA (Status) command only after waiting the proper delay time, defined in Section II, Table 2-2 and 2-3 or 100 milliseconds, if the preceding command affected the isolation relays, or 15 seconds if the preceding command was a confidence test (See paragraph 3-16).

- The response of the TLD 488–16 to a STA (Status) command is sent to the controller (Test Executive) in the form described below. The status is either reported as "normal" or as "abnormal". If conditions are normal, only one response message is sent. If conditions are abnormal, the controller (Test Executive) should send multiple status commands and talk addresses to the TLD 488–16 until all error messages are collected and transmitted.

- 3-29 CONDITION NORMAL. All "normal" response messages begin with an ASCII blank (space), followed by a carriage return and a line feed:

|         | BLANK MESSAGE |  |    | SAGE |

|---------|---------------|--|----|------|

| SYNTAX: | SP            |  | cr | lf   |

3-30 CONDITION ABNORMAL. All "abnormal" response messages begin with an ASCII "F", followed by a 2 digit ASCII integer code, followed by a text string describing the error condition. The 2 digit code used for TLD 488-16 is 07 (HALT) and is used by the controller (Test Executive) to take corrective action.

|         | ASCII "F" |    | ERROR MES | SAGE |        |    |      |    |    |

|---------|-----------|----|-----------|------|--------|----|------|----|----|

| SYNTAX: | [ F       | 07 | DCSnn     | SP   | (bbb): | SP | Text | cr | lf |

3-31 The next 3-digit code is the mnemonic abbreviation of the generic **type** device being controlled by the TLD 488-16 (DCS) followed by a two-digit numerical code to distinguish between multiple **units** controlled by the TLD 488-16 (0 to 15).

"bbb" indicates the origin of the message. There are two possibilities:

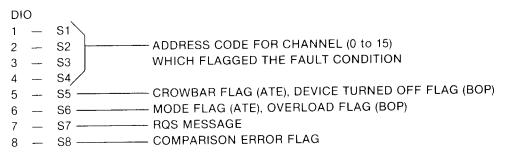

- A) bbb = DEV Device related error conditions as detected by the monitoring system of the power supply flags.